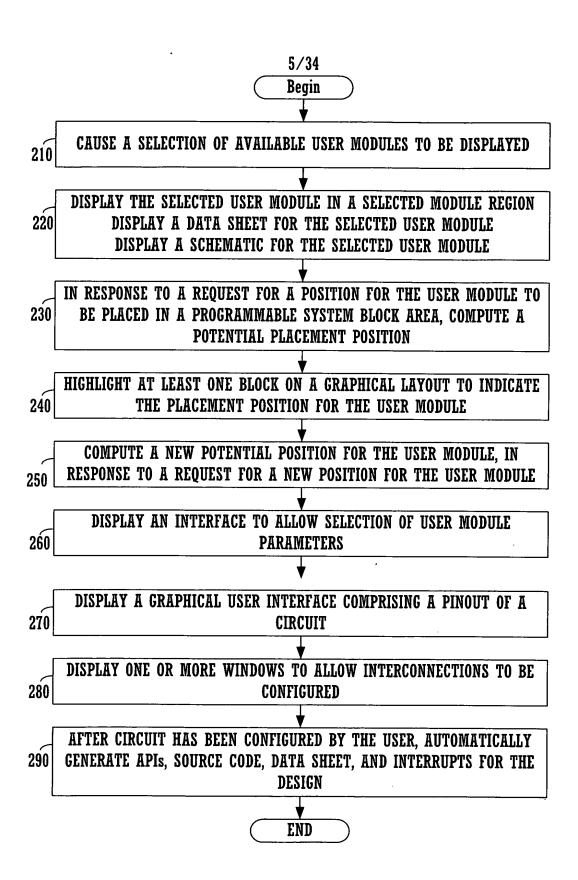

# FIGURE 2

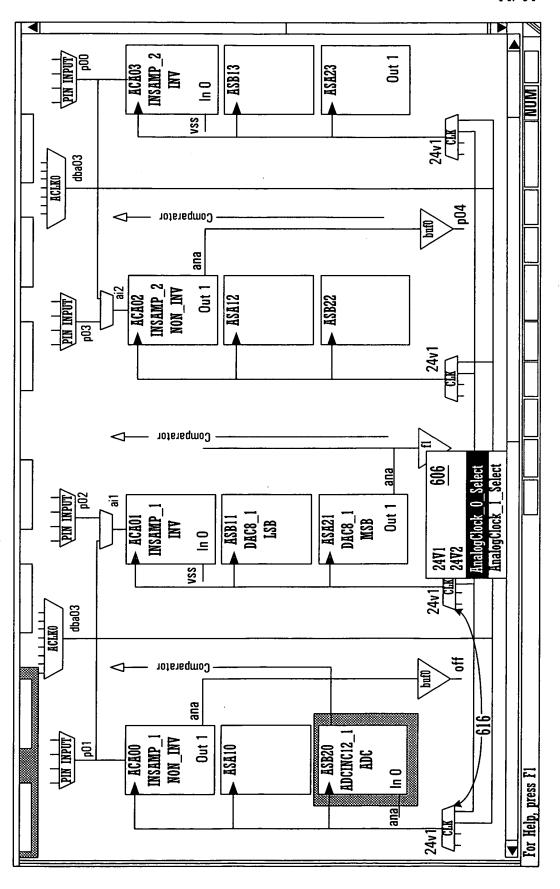

FIGURE 6B

17/34

#### **FIGURE 7A**

```

Instance name DAC8_1, User Module DAC8

Instance name DAC8_1, Block Name LSB(ASB11)

db

;DAC8_1_LSB_CRO

84h, 80h

db

85h, 80h

;DAC8_1_LSB_CR1

db

86h, 20h

;DAC8_1_LSB_CR2

db

87h, 30h

;DAC8_1_LSB_CR3

Instance name DAC8_1, Block Name MSB(ASA21)

;DAC8_1_MSB_CRO

94h, a0h

```

# FIGURE 7A (Continued)

```

db

95h, 41h

DAC8 1 MSB CR1

db

96h, a0h

;DAC8_1_MSB_CR2

db

97h, 30h

;DAC8_1_MSB_CR3

Instance name INSAMP_1, User Module INSAMP

Instance name INSAMP_1, Block Name INV(ACA01)

db

75h, beh

;INSAMP_1_INV_CRO

db

76h, 21h

;INSAMP_1_INV_CR1

db

77h, 20h

;INSAMP_1_INV_CR2

Instance name INSAMP_2, Block Name NON-INV(ACA00)

db

71h, 3ch

;INSAMP_1_NON_INV_CRO

db

72h, a1h

;INSAMP_1_NON_INV_CR1

db

73h, 20h

;INSAMP_1_NON_INV_CR2

Instance name INSAMP_2, User Module INSAMP

Instance name INSAMP_2, Block Name INV(ACA03)

db

;INSAMP_2_INV_CRO

7dh, ceh

db

7eh, 21h

;INSAMP_2_INV_CR1

db

7fh, 20h

;INSAMP_2_INV_CR2

Instance name INSAMP 2, Block Name NON INV(ACA02)

;INSAMP_2_NON_INV_CRO

db

79h, 2ch

db

7ah, a1h

;INSAMP_2_NON_INV_CR1

db

7bh, 20h

INSAMP 2 NON INV CR2

Instance name PWM16_1, User Module PWM16

Instance name PWM16_1, Block Name PWM16_LSB(DCA04)

db

30h, 01h

;PWM16_1_FUNC_LSB_REG

db

31h, c4h

;PWM16_1_INPUT_LSB_REG

db

32h, 00h

;PWM16_1_OUTPUT LSB REG

Instance name PWM16_1, Block Name PWM16_MSB(DCA05)

db

;PWM16_1_FUNC_MSB_REG

34h, 21h

db

35h, 34h

PWM16 1 INPUT MSB REG

db

36h, 05h

:PWM16 1 OUTPUT MSB REG

Instance name UART_1, User Module UART

Instance name UART_1, Block Name RX(DCA07)

db

3ch, 05h

;UART_1_RX_FUNC_REG

db

3dh, e1h

UART 1 RX INPUT REG

db

3eh, 00h

;UART_1_RX_OUTPUT_REG

Instance name UART_1, Block Name TX(DCA06)

db

38h, Odh

;UART_1_TX_FUNC_REG

db

;UART_1_TX_INPUT_REG

39h, 01h

db

3ah, 07h

;UART_1_TX_OUTPUT_REG

db

ffh

```

## FIGURE 7B

```

LoadConfigTBL_project_Bank0:

; Global Register values

60h, 14h

db

;AnalogColumnInputSelect register

db

63h, 05h

;AnalogReferenceControl register

65h, 00h

db

;AnalogSyncControl register

db

e6h, 00h

;DecimatorControl register

02h, 00h

db

;Port_0_Bypass register.

db

06h, f1h

;Port_1_Bypass register

db

0ah, 00h

;Port_2_Bypass register

db

0eh, 00h

;Port_3_Bypass register

db

12h, 00h

;Port_4_Bypass register

db

16h, 00h

;Port_5_Bypass register

Instance name ADCINC12_1, User Module ADCINC12

Instance name ADCINC12_1, Block Name ADC(ASB20)

Instance name ADCINC12_1, Block Name CNT(DBA01)

```

# FIGURE 7B (Continued)

```

21/34

db

27h, 00h

;ADCINC12_1_CounterCR0

db

25h, 00h

;ADCINC12 1 CounterDR1

db

26h, 00h

;ADCINC12_1_CounterDR2

Instance name ADCINC12_1, Block Name TMR(DBA00)

23h, 00h

db

;ADCINC12_1_TimerCR0

db

21h, 00h

;ADCINC12_1_TimerDR1

db

22h, 00h

;ADCINC12 1 TimerDR2

Instance name Counter16_1, User Module Counter16

Instance name Counter16, Block Name CNTR16_LSB(DBA02)

db

2bh, 00h

Counter16 1 CONTROL LSB REG

db

29h, 80h

;Counter16_1_PERIOD_LSB_REG

db

2ah, 64h

;Counter16_1_COMPARE_LSB REG

Instance name Counter16_1, Block Name CNTR16_MSB(DBA03)

db

2fh, 00h

;Counter16_1_CONTROL_MSB_REG

db

2dh, 00h

;Counter16_1_PERIOD_MSB_REG

db

2eh, 00h

Counter16_1_COMPARE MSB REG

Instance name DAC8_1, User Module DAC8

Instance name DAC8_1, Block Name LSB(ASB11)

Instance name DAC8_1, Block Name MSB(ASA21)

Instance name INSAMP 1, User Module INSAMP

Instance name INSAMP_1, Block Name INV(ACA01)

Instance name INSAMP 1, Block Name NON INV(ACA00)

Instance name INSAMP_2, User Module INSAMP

Instance name INSAMP_2, Block Name INV(ACA03)

Instance name INSAMP_2, Block Name NON_INV(ACA02)

Instance name PWM16_1, User Module PWM16

Instance name PWM16_1, Block Name PWM16_LSB(DCA04)

db

33h, 00h

;PWM16_1_CONTROL_LSB_REG

db

31h, 37h

;PWM16_1_PERIOD_LSB_REG

db

;PWM16_1_PWIDTH_LSB_REG

32h, 64h

Instance name PWM16_1, Block Name PWM16 MSB(DCA05)

đЬ

37h, 00h

:PWM16 1 CONTROL MSB REG

db

35h, 00h

;PWM16_1_PERIOD_MSB_REG

db

36h, 00h

PWM16 1 PWIDTH MSB REG

Instance name UART_1, User Module UART

Instance name UART_1, Block Name RX(DCA07)

db

3fh, 00h

;UART_1_RX_CONTROL_REG

db

3dh, 00h

;UART_1_

db

3eh, 00h

;UART_1_RX_BUFFER_REG

Instance name UART 1, Block Name TX(DCA06)

db

3bh, 00h

;UART_1_TX_CONTROL_REG

db

39h, 00h

;UART_1_TX_BUFFER_REG

db

3ah, 00h

;UART_1_

db

ffh

```

; Configuration file trailer Config.asm

```

; PSoCConfig.asm

22/34

This file is generated by the Device Editor on Application Generation.

; It contains code which loads the configuration data table generated in

the file ConfigTBL.asm

export LoadConfigInit

export_LoadConfigInit

Export LoadConfig_project

export_LoadConfig_project

Flag_CFG_MASK:

10h

;M8C flag register REG address bit

equ

mask

END_CONFIG_TABLE:

ffh

;end of config table indicator

equ

_LoadConfigInit:

LoadConfigInit:

lcall

LoadConfig_project

ret

;Load Configuration project

_LoadConfig_project:

LoadConfig_project:

or

F, FLAG CFG MASK

;set for

bank 1

A, >LoadConfigTBL_project_Bank1 ;load bank 1 table

mov

mov

X, <LoadConfigTBL_project_Bank1

call

LoadConfig

;load the

bank 1 values

and

F, ~FLAG_CFG_MASK

;switch

to bank 0

A, >LoadConfigTBL_project_Bank0; load bank 0 table

mov

mov

X, <LoadConfigTBL project Bank0

call

LoadConfig

;load the

bank 0 values

ret

LoadConfig

; This function is not exported. It assumes that the addresses of the table to be loaded

; is contained in the X and A registers as if a romx instruction is the next instruction

```

## FIGURE 8A

```

; to be executed, i.e. lower address in X and upper address in A. There is no return value.

LoadConfig:

LoadConfigLp:

X

;save config table address on stack

push

A

push

romx

;load config address

A, END_CONFIG_TABLE

;check for end of table

cmp

EndLoadConfig

; if so, end of load

jz

X, SP

;save the address away

mov

[X], A

mov

A

retieve the table address

pop

X

pop

X

inc

;advance to the data byte

NoOverFlow1

;check for overflow

inc

inc

;if so, increment MSB

NoOverFlow1:

PUSH

;save the config table address

X

again

push

A

romx

;load the config data

X, SP

retrieve the config address;

mov

X, [X]

mov

mov

reg[X], A

;write the config data

A

retieve the table address;

pop

X

pop

X

inc

;advance to the next

address

NoOverFlow2

;check for overflow

jnc

inc

A

; if so, increment MSB

NoOverFlow2:

jmp

LoadConfigLp

;loop back

EndLoadConfig:

A

;clean up the stack

pop

A

pop

ret

```

## FIGURE 8B

| **************                                  | 24/34                                              |  |

|-------------------------------------------------|----------------------------------------------------|--|

| 17<br>**********************************        | mov reg[ADCINC12_1_AtoDcr3],A                      |  |

| ;; ADCINC12.asm                                 | ret                                                |  |

| "<br>"                                          |                                                    |  |

| ;; Assembler source for the 12 bit Incremental  | "<br>"                                             |  |

| ;;A/D converter.                                | ;; Stop:                                           |  |

| ;;                                              | ;; SetPower:                                       |  |

| *****************************                   | ;; Removes power setting to the module's analog    |  |

| ****************                                | ;; Programmable System block                       |  |

| "                                               | ;; INPUTS: None                                    |  |

| export ADCINC12_1_Start                         | ;; OUTPUTS: None.                                  |  |

| export_ADCINC12_1_Start                         | "                                                  |  |

| export ADCINC12 1 SetPower                      | ADCINC12_1_Stop:                                   |  |

| export_ADCINC12_1_SetPower                      | _ADCINC12_1_Stop:                                  |  |

| export ADCINC12_1_Stop                          | and reg[ADCINC12_1_AtoDcr3],~03h                   |  |

| export_ADCINC12_1_Stop                          | ret                                                |  |

| export ADCINC12_1_GetSamples                    |                                                    |  |

| export_ADCINC12_1_GetSamples                    | "                                                  |  |

| export ADCINC12_1_StopAD                        | ;; Get_Samples:                                    |  |

| export_ADCINC12_1_StopAD                        | ;; SetPower:                                       |  |

| export ADCINC12_1_flsdata                       | ;; Starts the A/D convertor and will place data in |  |

| export_ADCINC12_1_flsdata                       | ;;memory. A flag                                   |  |

| export ADCINC12_1_GetData                       | ;; is set whenever a new data value is available.  |  |

| export_ADCINC12_1_GetData                       | ;; INPUTS: A passses the number of samples (0      |  |

| export ADCINC12_1_ClearFlag                     | ;;is continuous).                                  |  |

| export_ADCINC12_1_ClearFlag                     | ;; OUTPUTS: None.                                  |  |

| ,                                               | "                                                  |  |

| include "ADCINC12_1.inc"                        | ADCINC12_1_GetSamples:                             |  |

| include "m8c.inc"                               | _ADCINC12_1_GetSamples:                            |  |

|                                                 | mov [ADCINC12_1_blncrC],A ;number                  |  |

| LowByte: equ 1                                  | ;of samples                                        |  |

| HighByte: equ 0                                 | or reg[INT_MSK1],(ADCINC12_1_TimerMask             |  |

|                                                 | ADCINC12_1_CounterMask)                            |  |

| "<br>"                                          | enable both interrupts;                            |  |

| ;; Start:                                       | Mov[ADCINC12_1_cTimerU],0 ;Force the               |  |

| ;; SetPower:                                    | Timer to do one cycle of rest;                     |  |

| ;; Applies power setting to the module's analog | or reg{ADCINC12_1_AtoDcr3],10h ;force the          |  |

| ;; Programmable System block                    | ;Integrator into reset                             |  |

| ;; INPUTS: A contains the power setting         | _mov[ADCINC12_1_cCounterU],ffh ;Initialize         |  |

| ;; OUTPUTS: None.                               | ;Counter                                           |  |

| "                                               |                                                    |  |

| ADCINC12_1_Start:                               | mov[ADCINC12_1_TimerDR1],ffh                       |  |

| _ADCINC12_1_Start:                              | mov[ADCINC12_1_CounterDR1],ffh                     |  |

| ADCINC12_1_SetPower:                            | mov[ADCINC12_1_TimerCR0],01h ;enable               |  |

| _ADCINC12_1_SetPower:                           | ;the Timer                                         |  |

| and A,O3h                                       | mov[ADCINC12_1_fincr],00h ;A/D Data                |  |

| or A,f0h                                        | ;Ready Flag is reset                               |  |

```

25/34

(Continued)

;; StopAD:

;; Completely shuts down the A/D in an orderly

ADCINC12 1 iGetData:

;;manner. Both the

_ADCINC12_1_iGet Data:

;; Timer and Counter Interrupts are disabled.

mov X,[(ADCINC12_1_ilncr+HighByte)]

;; INPUTS: None.

mov A,[(ADCINC12_1 ilncr+LowByte)]

;; OUTPUTS: None.

ADCINC12_1_StopAD:

ADCINC12 1 StopAD:

;; ClearFlag:

mov[ADCINC12_1_TimerCR0],00h

;; clears the data ready flag.

disable the Timer

;; INPUTS: None

mov[ADCINC12_1_CounterCR0],00h

;; OUTPUTS: None.

disable the Counter

nop

ADCINC12 1 ClearFlag:

nop

_ADCINC12_1_ClearFlag:

and

mov [ADCINC12_1_flncr],00h

reg[INT_MSK1],~(ADCINC12_1_TimerMask |

ADCINC12_1_CounterMask)

ret

;Disable both

ADCINC12_1_API_End:

;;interrupts

or reg[ADCINC12_1_AtoDc3],10h

;reset

;;Intergrator

ret

:: flddata:

;; Returns the status of the A/D Data

;; is set whenever a new data value is available.

:: INPUTS: None.

;; OUTPUTS: A returned data status A=:0 no

;;data available

!=: 0 data available.

ADCINC12_1_flsdata:

_ADCINC12_1_flsdata:

movA,[ADCINC12_1_fincr]

ret

:: iGetData:

;; Returns the status from the A/D. Does not

;;check if data is

;; available.

;; is set whenever a new data value is available.

;; INPUTS: None.

;; OUTPUTS: X:A returns the A/D data value.

```

```

***************

// ADCINC12_1.h for the 12 bit incremental A/D converter

//

// C declarations for the ADCINC12 User Module

//

//

// ************************

//***************************

#define ADCINC12 1 OFF

#define ADCINC12 1 LOWPOWER

1

#define ADCINC12_1_MEDPOWER

2

#define ADCINC12 1 HIGHPOWER

#pragma fastcall ADCINC12_1_Start

#pragma fastcall ADCINC12_1_SetPower

#pragma fastcall ADCINC12_1_GetSamples

#pragma fastcall ADCINC12_1_StopAD

#pragma fastcall ADCINC12_1_Stop

#pragma fastcall ADCINC12_1_flsData

#pragma fastcall ADCINC12 1 iGetData

#pragma fastcall ADCINC12_1_ClearFlag

extern void ADCINC12_1_Start(char power);

extern void ADCINC12 1 SetPower(char power);

extern void ADCINC12_1_GetSamples(char chout);

extern void ADCINC12 1 StopAD(void);

extern void ADCINC12 1 Stop(void);

extern char ADCINC12_1_flsData(void);

extern int ADCINC12_1_iGetData(void);

extern void ADCINC12_1_ClearFlag(void);

```

```

ADCINC12_1.inc for the 12 bit incremental A/D converter

Assembler declarations for the ADCINC12 User Module

ADCINC12 1 AtoDcr0:

90h

equ

ADCINC12_1_AtoDcr1:

91h

equ

ADCINC12_1_AtoDcr2:

equ

92h

ADCINC12 1 AtoDcr3:

93h

equ

ADCINC12_1_CounterFN:

24h

equ

ADCINC12_1_CounterSL:

equ

25h

ADCINC12_1_CounterOS:

26h

equ

ADCINC12 1 CounterDR0:

24h

equ

ADCINC12_1_CounterDR1:

equ

25h

ADCINC12 1 CounterDR2:

26h

equ

ADCINC12 1 CounterCR0:

27h

equ

ADCINC12 1 TimerFN:

20h

equ

ADCINC12_1_TimerSL:

21h

equ

ADCINC12_1_TimerOS:

22h

equ

ADCINC12 1 TimerDR0:

20h

equ

ADCINC12 1 TimerDR1:

21h

equ

ADCINC12 1 TimerDR2:

22h ·

equ

ADCINC12 1 TimerCR0:

23h

equ

ADCINC12_1_TimerMask:

equ

01h

ADCINC12_1_CounterMask:

02h

equ

ADCINC12 1 OFF:

0

ADCINC12_1_LOWPOWER:

1

equ

ADCINC12_1_MEDPOWER:

2

equ

ADCINC12 1 HIGHPOWER:

3

equ

ADCINC12_1_NUMBITS:

12

equ

```

```

ADCINC12int.asm

;; Assembler source for interrupt routines the 12 bit Incremental

;;A/D converter.

export ADCINC12_1_CNT_INT

export_ADCINC12_1_TMR_INT

include "ADCINC12_1.inc"

include "m8c.inc"

Area bss(RAM)

ADCINC12 1 cTimerU:

BLK 1

The upper byte of the Timer

ADCINC12_1_cCounterU: BLK 1

The Upper byte of the Counter

ADCINC12_1_ilncr:

ADCINC12_1_ilncr:

BLK 2

;A/D value

ADCINC12 1 flncr

ADCINC12_1_flncr:

BLK 1

;Data Valid Flag

ADCINC12_1_blncrC:

BLK 1

;# of times to run A/D

area text(ROM,REL)

export_ADCINC12_1_cTimerU

export ADCINC12_1_cCounterU

export_ADCINC12_1_ilncr

export ADCINC12_1_ilncr

export_ADCINC12_1_flncr

export ADCINC12 1 flncr

export_ADCINC12_1_blncrC

LowByte: equ 1

HighByte: equ 0

;; CNT_INT:

;; Decrement the upper (software) half on the counter whenever the

;; lower (hardware) half of the counter underflows.

;; INPUTS:: None.

;; OUTPUTS: None.

ADCINC12_1_CNT_INT:

dec[ADCINC12_1_cCounterU]

reti

FIGURE 12A

```

```

; if(A/D has been in reset mode)

mov reg[ADCINC12_1_CounterCR0],01h

;Enable Counter

and reg[ADCINC12_1_AtoDcr3],~10h

Enable Analog Counter

mov reg[ADCINC12_1_cTimerU],((1<<(ADCINC12_1_NUMBITS-6))-1)

This will be the real counter value

reti

else2::(A/D has been in integrate mode)

mov reg[ADCINC12_1_CounterCR0],00h

;disable Counter

or F,01h

:Enable the interrupts

Good place to add code to switch inputs for multiplexed input to ADC

or reg[ADCINC12_1_AtoDcr3],10h; Reset Integrator

mov [(ADCINC12_1_ilncr+LowByte)],ffh

mov [(ADCINC12_1_ilncr+HighByte)],(ffh-(ADCINC12_1_NUMBITS-7)))

push A

mov A, reg[ADCINC12_1_CounterDR0],01h ;read Counter

mov A, reg[ADCINC12_1_CounterDR2],01h; now you really read the data

sub[(ADCINC12 1 ilncr+LowByte)],A

mov A, reg[ADCINC12 1 cCounterU]

sbb[(ADCINC12_1_ilncr+HighByte)],A

pop A

cmp[(ADCINC12_1_ilncr+HighByte)],(1<<(ADCINC12_1_NUMBITS-7))

inz endif10

; if(max positive value)

dec[(ADCINC12_1_ilncr+HighByte)]

mov[(ADCINC12_1_ilncr+LowByte)],ffh

endif10:

asr[(ADCINC12_1_ilncr+HighByte)]

;divide by 4

rrc[(ADCINC12 1 ilncr+LowByte)]

asr[(ADCINC12_1_ilncr+HighByte)]

rrc[(ADCINC12 1 ilncr+LowByte)]

mov[ADCINC12 1 flncr].01h

;set AD data flag

```

## FIGURE 12B

```

; User code here for interrupt system.

cmp[ADCINC12_1_blncrC],00h

jz endif3

; if(ADCINC12_1_blncrC is not zero)

dec[ADCINC12_1_blncrC]

jnz endif4

; if(ADCINC12_1_blncrC has decremented down to zero to 0))

mov reg[ADCINC12_1_TimerCR0],00h

disable the Timer

mov reg[ADCINC12_1_CounterCR0],00h

; disable the Counter

nop

and reg[INT_MSK1],~(ADCINC12_1_TimerMask | ADCINC12_1_CounterMask)

; disable both interrupts

or reg[ADCINC12_1_AtoDcr3],10h

;reset Integrator

reti

endif4:;

endif3:;

endif2:;

mov [ADCINC12_1_cTimerU],00h

;Set Timer for one cycle of reset

mov [ADCINC12_1_cCounterU],ffh

;Set Counter hardware for easy enable

mov reg[ADCINC12_1_CounterDR1],ffh

reti

endifl:;

ADCINC12_1_APIINT_End: A/D converter

```

# FIGURE 12B (Continued)

### FIGURE 13A

| 1351                    | 1352                      | 1353                      |

|-------------------------|---------------------------|---------------------------|

| boot.asm Interrupt Name | Data Sheet Interrupt Name | Туре                      |

| Start                   | Reset                     | Fixed                     |

| Interrupt1              | Supply Monitor            | Fixed                     |

| Interrupt2              | DBA00                     | Programmable System Block |

| Interrupt3              | DBA01                     | Programmable System Block |

| Interrupt4              | DBA02                     | Programmable System Block |

| Interrupt5              | DBA03                     | Programmable System Block |

| Interrupt6              | DCA04                     | Programmable System Block |

| Interrupt7              | DCA05                     | Programmable System Block |

| Interrupt8              | DCA06                     | Programmable System Block |

| Interrupt9              | DCA07                     | Programmable System Block |

| Interrupt10             | Analog Column 0           | Programmable System Block |

| Interrupt 1 1           | Analog Column 1           | Programmable System Block |

| Interrupt12             | Analog Column 2           | Programmable System Block |

| Interrupt13             | Analog Column 3           | Programmable System Block |

| Interrupt14             | GPI0                      | Fixed                     |

| Interrupt15             | SLEEP TIMER               | Fixed                     |

# FIGURE 13B

FIGURE 14